# **Datasheet**

# FLIP51 MCU+RF

Beken Corporation Building 41, 1387 Zhangdong Road, Zhangjiang High-Tech Park, Pudong New District, Shanghai, China

> Tel: (86)21 51086811 Fax: (86)21 60871089

This document contains information that may be proprietary to, and/or secrets of, Beken Corporation. The contents of this document should not be disclosed outside the companies without specific written permission.

Disclaimer: Descriptions of specific implementations are for illustrative purpose only, actual hardware implementation may differ.

# Revision History

| Version | Date         | Author(s) | Description           |

|---------|--------------|-----------|-----------------------|

| 0.1     | Nov. 20,2014 | Lizhen    | Initial flash version |

| 0.2     | Mar. 20,2015 | Lizhen    | Update version        |

|         |              |           |                       |

|         |              |           |                       |

|         |              |           |                       |

|         |              |           |                       |

|         |              |           |                       |

|         |              |           |                       |

|         |              |           |                       |

# **Table of Contents**

| 1  | Introdu   | uction                                         | 9    |

|----|-----------|------------------------------------------------|------|

| 2  | Feature   | <u>,                                      </u> | 9    |

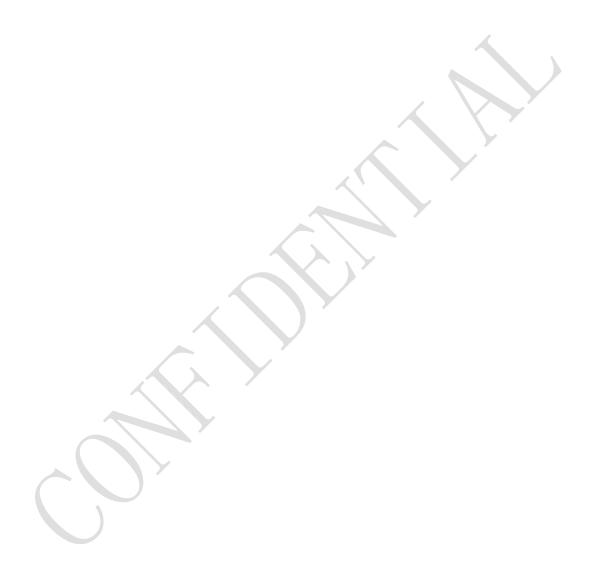

| 3  | Block I   | Diagram                                        | 10   |

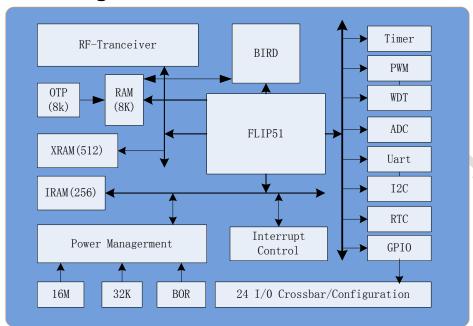

| 4  | PIN inf   | formation                                      | 11   |

|    | 4.1 BK    | 2461_QFN24                                     | 11   |

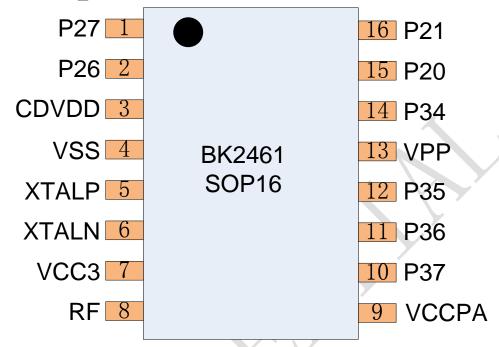

|    | 4.2 BK    | 2461_SOP16                                     | 13   |

| 5  |           | Micro-Controller                               |      |

|    | 5.1 Inst  | truction Set                                   | 14   |

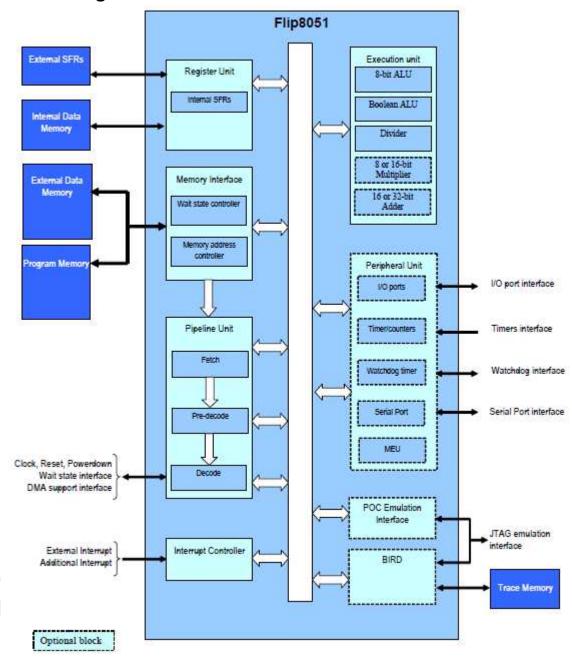

|    | 5.2 MC    | CU diagram                                     | 15   |

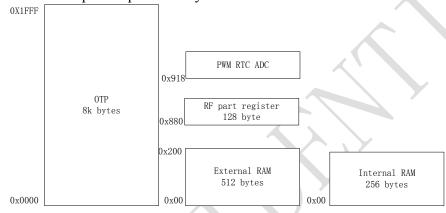

| 6  | FLIP8(    | 051 address space                              | 17   |

|    | 6.1 Ove   | erview                                         | 17   |

|    | 6.2 Pro   | gram Memory (CODE space)                       | . 17 |

|    | 6.3 Ext   | ernal Data Memory (XDATA space)                | 17   |

|    | 6.4 Inte  | ernal Data Memory (IDATA space)                | 18   |

|    | 6.4.1     | Internal Data memory organization              | 18   |

|    | 6.4.2     | Internal ram: lower 128 byes                   | 19   |

|    | 6.4.3     | Internal Ram: Upper 128 Bytes                  | 19   |

|    | 6.4.4     | The Stack and the stack pointer                | 19   |

|    | 6.4.5     | Special Function Registers                     | 20   |

|    | 6.4.6     | SFR table for MCU part                         | 24   |

| 7  | Power     | management                                     | 26   |

|    | 7.1 Pov   | wer Control Register                           | 26   |

|    | 7.2 Wo    | ork State                                      | 27   |

|    | 7.2.1     | IDLE MODE                                      | 27   |

|    | 7.2.2     | SLEEP MODE                                     | 27   |

|    | 7.2.3     | DEEP SLEEP MODE                                |      |

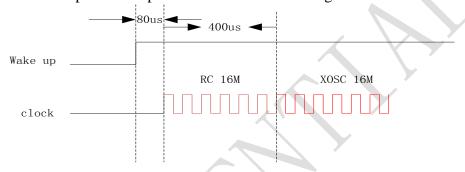

|    | 7.2.4     | Wake Up                                        | 28   |

| 8  | Clock s   | system                                         | 28   |

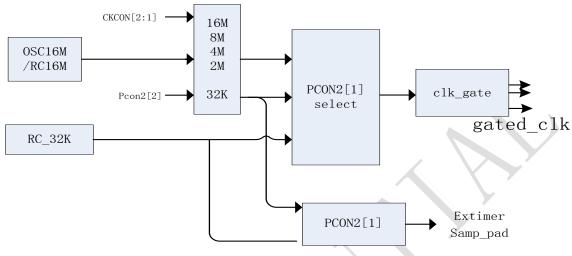

|    | 8.1 Sys   | stem clock topology                            | 28   |

|    | 8.2 Per   | ipherals clock management                      | 29   |

| 9  | Reset s   | ystem                                          | 30   |

| 1( |           | pt system                                      | 31   |

|    | 10.1 7.1  | Introduction                                   | 31   |

|    |           | Interrupt source                               |      |

|    | 10.1.2    | Int0_n and int1_n                              | 32   |

|    |           | Intnmi interrupt                               |      |

|    | 10.1.4    | Additional interrupts                          | 33   |

|    |           | Timer Interrupts                               |      |

|    |           | Serial Port Interrupt                          |      |

|    |           | TRAP interrupt                                 |      |

|    |           | errupt enable                                  |      |

|    |           | errupt priority                                |      |

|    | 10.4 Inte | errupt blocking conditions                     | 37   |

|    |           |                                                |      |

| 11 Periphe | ral module                           | 38  |

|------------|--------------------------------------|-----|

| 11.1 OV    | ERVIEW                               | 38  |

| 11.2 UA    | RT                                   | 38  |

| 11.2.1     | Serial port overview                 | 38  |

| 11.2.2     | Operation mode                       | 38  |

| 11.2.3     | Programming the Baud Rate            | 40  |

|            | Serial port registers                |     |

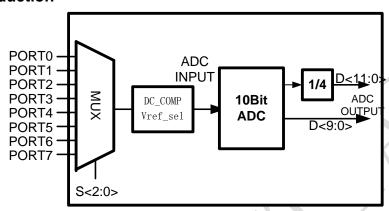

| 11.1 AD    | C                                    | 43  |

| 11.1.1     | introduction                         | 43  |

| 11.1.2     | Register explain                     | 43  |

| 11.1.3     | Sample rate:                         | 44  |

| 11.1.4     | ADC usage                            | 44  |

| 11.2 PW    | M                                    | 45  |

| 11.2.1     | OVERVIEW                             | 45  |

| 11.2.2     | FUNCTIONAL DESCRIPTION               | 45  |

|            | Frequency of PWM                     |     |

|            | master                               |     |

|            | Overview                             |     |

|            | List of I2CM register                |     |

|            | I2C frame data format                |     |

| 11.3.4     | Acknowledge                          | 52  |

|            | Clock synchronization and wait state |     |

|            | Master mode: Transmission            |     |

| 11.3.7     | Master mode: Reception               | 58  |

| 11.3.8     | Stop and Repeated Start              | 58  |

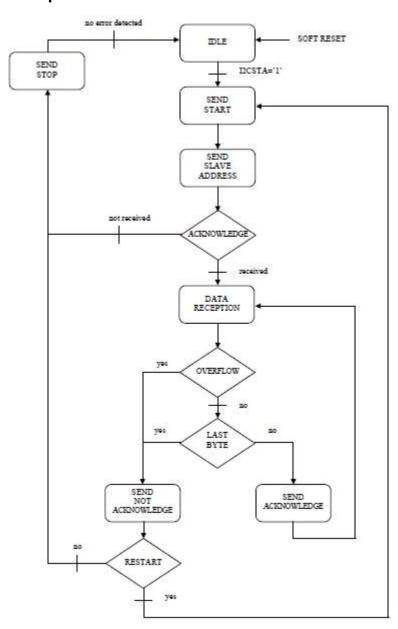

|            | Reception FSM                        |     |

| 11.3.10    | Data Handling                        | 60  |

| 11.3.11    | Software Reset                       | 61  |

|            | _timer                               |     |

|            |                                      |     |

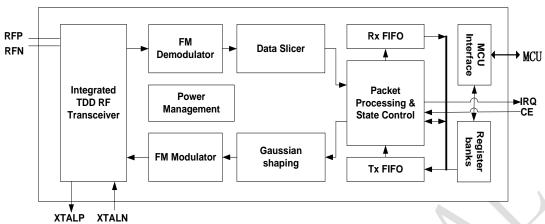

|            | 1 RF transceiver                     |     |

|            | neral Description                    |     |

|            | previations                          |     |

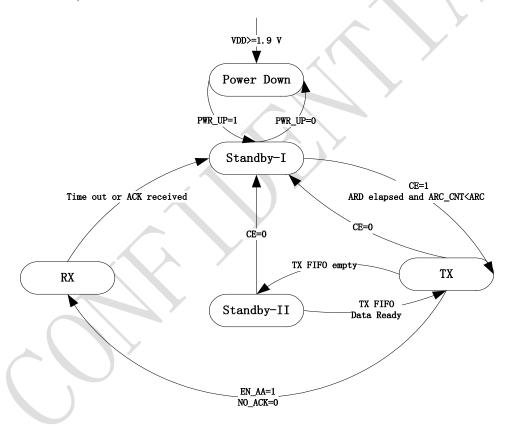

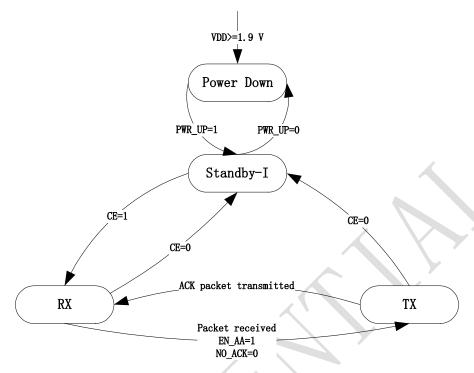

|            | te Control                           |     |

| 12.3.1     | State Control Diagram                |     |

|            | Power Down Mode                      |     |

|            | Standby-I Mode                       |     |

|            | Standby-II Mode                      |     |

|            | TX Mode                              |     |

|            | RX Mode                              |     |

|            | ket Processing.                      |     |

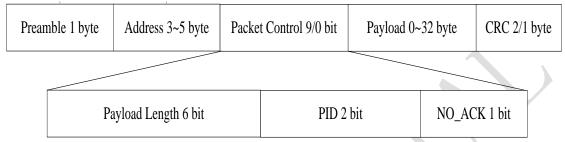

|            | Packet Format                        |     |

|            | Packet Handling                      |     |

|            | a and Control Interface              |     |

|            | TX/RX FIFO                           |     |

|            | Interrupt                            |     |

| 14.5.4     | 111tt 11tt 1pt                       | / + |

| 1  | 2.6 RF Command                  | 75 |

|----|---------------------------------|----|

| 1  | 2.7 Register Map                | 77 |

|    | 12.7.1 Digital Register         |    |

|    | 12.7.2 Analog Register          |    |

|    | 12.7.3 TX power control setting |    |

| 13 | Typical Application Schematic   | 88 |

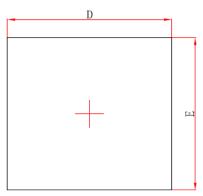

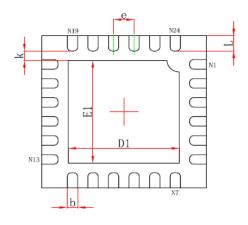

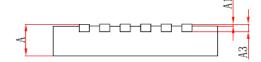

| 14 | Package Information             | 89 |

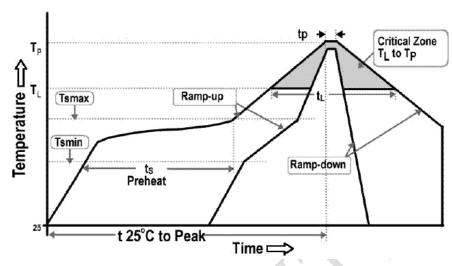

| 15 | Solder Reflow Profile           | 93 |

| 16 | Order Information               | 94 |

| 17 | Solder Reflow Profile           | 94 |

| 18 | Contact Information             | 95 |

# **List of Figures**

| FIGURE 1BK2461 BLOCK DIAGRAM                                | 10 |

|-------------------------------------------------------------|----|

| FIGURE 2 BK2461-QFN                                         | 11 |

| FIGURE 3 BK2461-SOP                                         | 13 |

| FIGURE 4 FLIP51 ARCHITECTURE                                | 15 |

| FIGURE 5 <b>FLIP51 SPACE</b>                                | 17 |

| FIGURE 6 INTERNAL DATA MEMORY                               | 19 |

| FIGURE 7 INTERNAL RAM LOWER 128 BYTES                       | 19 |

| FIGURE 8 WAKE UP PROCESS                                    | 28 |

| FIGURE 9 CLOCK TOPOLOGY                                     | 29 |

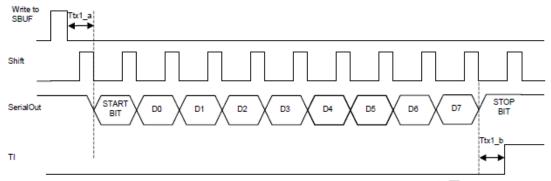

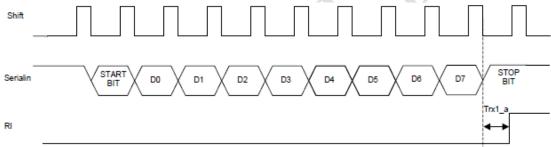

| FIGURE 10 SERIAL TRANSMIT MODE 1                            | 39 |

| FIGURE 11 SERIAL RECEIVE MODE 1                             |    |

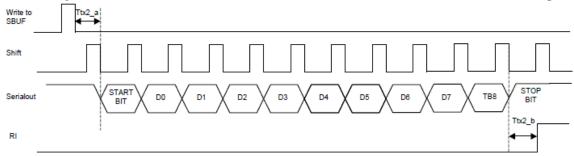

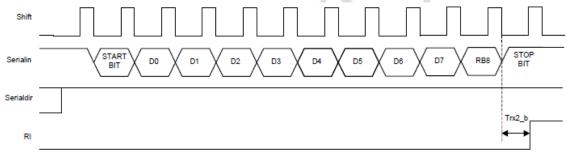

| FIGURE 12 SERIAL TRANSMIT MODE 2                            |    |

| FIGURE 13 SERIAL RECEIVE MODE 2                             |    |

| FIGURE 14 <i>ADC</i>                                        |    |

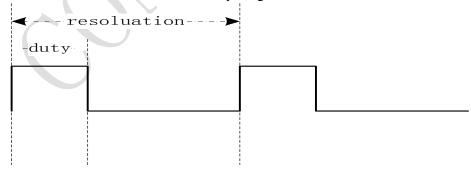

| FIGURE 15 PWM PARAMETER                                     |    |

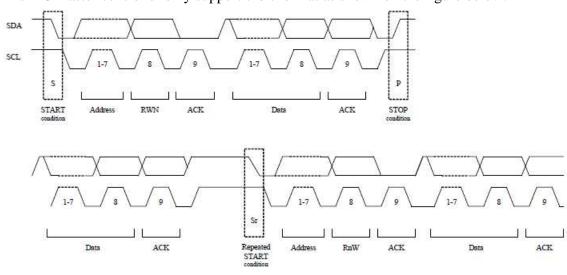

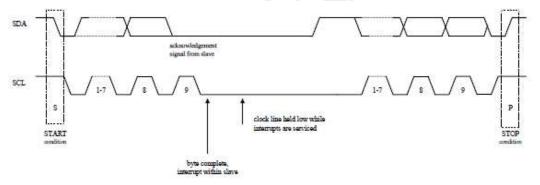

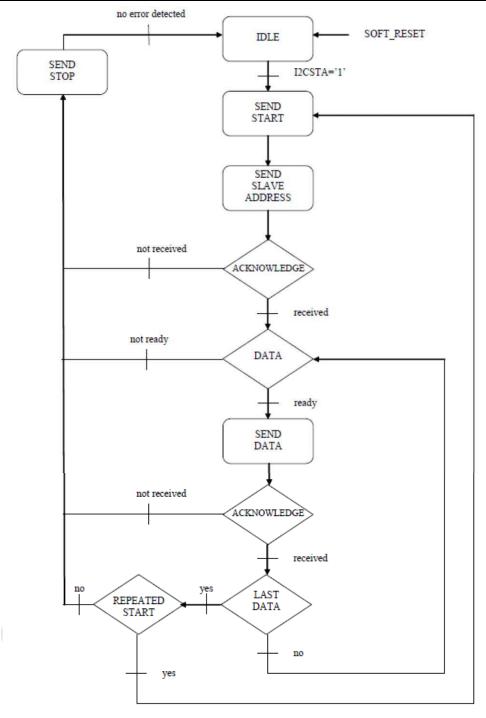

| FIGURE 16 COMPLETE DATA TRANSFER                            |    |

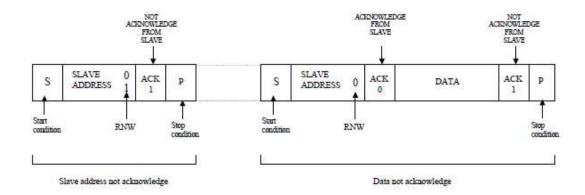

| FIGURE 17 "NOT ACKNOWLEDGE" BY SLAVE                        |    |

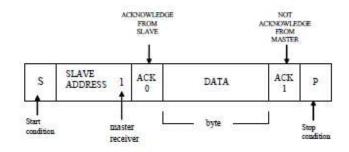

| FIGURE 18 "NOT ACKNOWLEDGE" BY MASTER (END OF TRANSMISSION) |    |

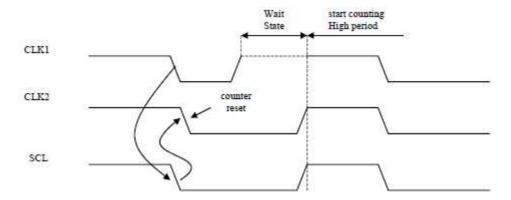

| FIGURE 19 CLOCK SYNCHRONIZATION AS HANDSHAKE                |    |

| FIGURE 20 CLOCK SYNCHRONIZATION                             |    |

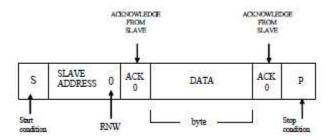

| FIGURE 21 TYPICAL TRANSMISSION                              |    |

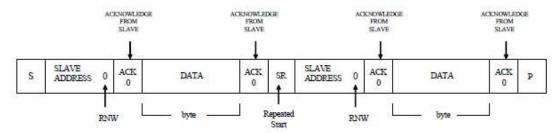

| FIGURE 22 REPEATED START OR STOP CONDITION AFTER LAST BYTE  |    |

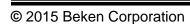

| FIGURE 23 TRANSMISSION FSM                                  |    |

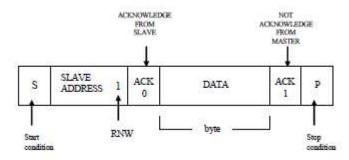

| FIGURE 24 TYPICAL RECEPTION                                 | 58 |

| FIGURE 25 REPEATED START OR STOP CONDITION AFTER LAST BYTE  | 59 |

| FIGURE 26 RECEPTION FSM                                     |    |

| FIGURE 27 BK2461 RF BLOCK DIAGRAM                           |    |

| FIGURE 28 PTX (PRIM_RX=0) STATE CONTROL DIAGRAM             | 67 |

| FIGURE 29 PRX (PRIM_RX=1) STATE CONTROL DIAGRAM             | 68 |

| FIGURE 30 PACKET FORMAT                                     | 70 |

| FIGURE 31 CLASSIFICATION REFLOW PROFILE                     | 93 |

# List of tables

| TABLE 1 PIN DEFINITION                                                |      |

|-----------------------------------------------------------------------|------|

| TABLE 2 PIN DEFINITION                                                |      |

| TABLE 3 SPECIAL FUNCTION REGISTERS MEMORY MAP                         |      |

| TABLE 4 CORE SFRS                                                     |      |

| TABLE 5 ADDITIONAL INTERRUPT SFRS                                     | 24   |

| TABLE 6 I/O PORTS SFRS                                                |      |

| TABLE 7 SERIAL PORT SFRS                                              | 25   |

| TABLE 8 TIMERS SFRS                                                   | 26   |

| TABLE 9 BIRD SFRS                                                     |      |

| TABLE 10 POWER MANAGEMENT REGISTER                                    | 26   |

| TABLE 11 CLOCK ENABLE REGISTER                                        | 29   |

| TABLE 12 INTERRUPT SOURCES                                            | 32   |

| TABLE 13 TIMER/COUNTER CONTROL REGISTER (TCON LOW)                    | . 33 |

| TABLE 14 ADDITIONAL INTERRUPT REGISTERS                               | . 33 |

| TABLE 15 ADDITIONAL INTERRUPT FLAG REGISTER (AIF)                     | . 34 |

| TABLE 16 INTERRUPT ENABLE 0 REGISTER (IEO)                            | 35   |

| TABLE 17 ADDITIONAL INTERRUPT ENABLE REGISTER (AIE)                   | 35   |

| TABLE 18 INTERRUPT PRIORITY LEVELS AND VECTOR ADDRESSES               | . 36 |

| TABLE 19 INTERRUPT PRIORITY WITHIN A SAME PRIORITY LEVEL (0 OR 1)     | . 37 |

| TABLE 20 INTERRUPT PRIORITY REGISTER (IP)                             |      |

| TABLE 21 ADDITIONAL INTERRUPT PRIORITY REGISTER (AIP)                 | . 37 |

| TABLE 22 SERIAL PORT REGISTERS                                        |      |

| TABLE 23 SERIAL PORT CONTROL REGISTER (SCON)                          | 42   |

| TABLE 26 ADC REGISTER                                                 |      |

| TABLE 27 ADC REGISTER                                                 |      |

| TABLE 28 ADC 的 SFR                                                    | 44   |

| TABLE 29 ADC REGISTER                                                 | 44   |

| TABLE 30 ADC REGISTER                                                 |      |

| TABLE 31 ADC ANALOG REGISTER                                          |      |

| TABLE 24 PWM REGISTER ADDRESS                                         |      |

| TABLE 25 I2CM REGISTER                                                |      |

| TABLE 26 I2CM CONTROL REGISTER (MCON)                                 |      |

| TABLE 27 I2CM RECEIVE REGISTER (MRXBUF)                               |      |

| TABLE 28 I2CM TRANSMIT BUFFER (MTXBUF)                                |      |

| TABLE 29 I2CM MPRESC REGISTER                                         |      |

| TABLE 30 I2CM STATUS REGISTER 0 (MSTATO)                              |      |

| TABLE 31 I2CM STATUS REGISTER 1 (MSTATI)                              | 49   |

| TABLE 32 I2CM INTERRUPT ENABLE REGISTER 0 (MIENO)                     |      |

| TABLE 33 I2CM INTERRUPT ENABLE REGISTER 1 (MIEN1)                     |      |

| TABLE 33 I2CM (ALL ADDRESS REGISTER (MCADDR)                          |      |

| TABLE 35 RESERVED ADDRESSES FOR IZCANSACTIONS                         |      |

| TABLE 36 RTC REGISTER                                                 |      |

| TABLE 30 WATCH DOG REGISTER                                           |      |

| TABLE 20 WATCH DOG REGISTER  TABLE 21 THE PRESCALE OF WATCH DOG CLOCK |      |

| TABLE 21 THE PRESCALE OF WATCH DOG CLOCK                              |      |

|                                                                       |      |

| TABLE 38 DIGITAL REGISTER                                             |      |

| TABLE 39 REGISTER BANK 1                                              |      |

| TABLE 40 TX POWER SETTING                                             |      |

| TABLE 41 SOLDER REFLOW PROFILE                                        | 93   |

## 1 Introduction

The BK2461 is a RF SOC chip, which embedded the newest FLIP51 processor.

### 2 Feature

- 1.9 V to 3.6 V power supply

- FLIP51 MCU compatible with 8051

- A 4-stage pipeline architecture that enables to execute most of the instructions in a single clock cycle.

- 8k bytes OTP for program

- 256 Bytes IRAM and 512k Bytes SRAM

- Embedded three Timer/Counter

- Support UART I2C interface

- low power consumption, embedded with 32k RC oscillator

- Total 9/18 GPIO available

- The most 5 PWM available

- The embedded BIRD (Built-In Real-time Debugger) system for online debug

- 8+1 channel ADC embedded

- Integrated 2.4G RF transceiver

- The max output power can be 12DBm

- low power consumption, embedded with 32k RC oscillator

# 3 Block Diagram

Figure 1BK2461 Block Diagram

## 4 PIN information

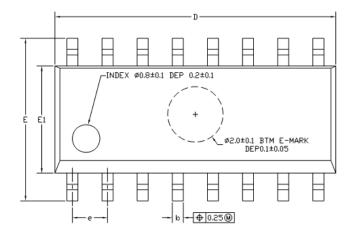

## 4.1 BK2461\_QFN24

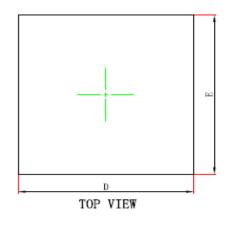

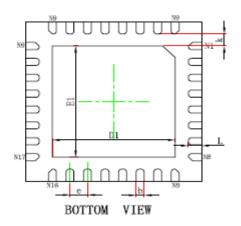

Figure 2 BK2461-QFN

| Num. | Name  | Pin Function         | Description                                                                 |  |

|------|-------|----------------------|-----------------------------------------------------------------------------|--|

| 1    | VCC3  | Power supply         | 3v supply                                                                   |  |

| 2    | RF    | Antenna input/output |                                                                             |  |

| 3    | VCCPA | Analog output        |                                                                             |  |

| 4    | P3.7  | Digital I/O          | General I/O, ADC input                                                      |  |

| 5    | P3.6  | Digital I/O          | General I/O, ADC input                                                      |  |

| 6    | P3.5  | Digital I/O          | General I/O, ADC input                                                      |  |

| 7    | VPP   | Power supply         | Mode select and 6.5V power supply<br>for OTP burning, or P12<br>output(PWM) |  |

| 8    | P3.4  | Digital I/O          | General I/O, ADC input                                                      |  |

| 9    | P3.3  | Digital I/O          | General I/O, ADC input                                                      |  |

| 10 | P3.2  | Digital I/O   | General I/O, ADC input          |

|----|-------|---------------|---------------------------------|

| 11 | P1.1  | Digital I/O   | General I/O, external interrupt |

| 12 | P3.1  | Digital I/O   | General I/O, ADC input          |

| 13 | P2.0  | Digital I/O   | General I/O, or input for UART  |

| 14 | P3.0  | Digital I/O   | General I/O, ADC input          |

| 15 | P2.1  | Digital I/O   | General I/O, or output for UART |

| 16 | P2.2  | Digital I/O   | General I/O, or I2C SCL         |

| 17 | P2.3  | Digital I/O   | General I/O, or I2C SDA         |

| 18 | P2.4  | Digital I/O   | General I/O, or PWM, or JTAG    |

| 19 | P2.5  | Digital I/O   | General I/O, or PWM, or JTAG    |

| 20 | P2.7  | Digital I/O   | General I/O, or PWM, or JTAG    |

| 21 | P2.6  | Digital I/O   | General I/O, or PWM, or JTAG    |

| 22 | CDVDD | Analog output | power output, connected with    |

|    |       |               | decoupling CAP                  |

| 23 | XTALP | Analog output | Oscillator output               |

| 24 | XTALN | Analog input  | Oscillator input                |

**Table 1 PIN definition**

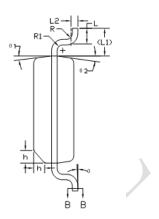

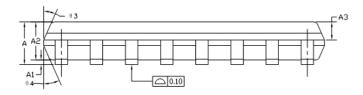

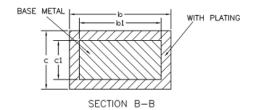

## 4.2 BK2461\_SOP16

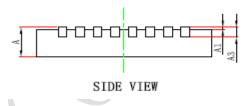

Figure 3 BK2461-SOP

| NO. | Name  | Pin Function                                              | Description                                                      |

|-----|-------|-----------------------------------------------------------|------------------------------------------------------------------|

| 1   | P2.7  | Digital I/O                                               | General I/O, or PWM                                              |

| 2   | P2.6  | Digital I/O General I/O, or PWM                           |                                                                  |

| 3   | CDVDD | Analog output power output, connected with decoupling CAP |                                                                  |

| 4   | VSS   | ground                                                    |                                                                  |

| 5   | XTALP | Analog output                                             | Oscillator output                                                |

| 6   | XTALN | Analog input                                              | Oscillator input                                                 |

| 7   | VCC3  | Power supply                                              | 3v supply                                                        |

| 8   | RF    | Antenna input/output                                      |                                                                  |

| 9   | VCCPA | Analog output                                             | PA power output, connected with decoupling CAP                   |

| 10  | P3.7  | Digital I/O                                               | General I/O, ADC input ,OTP download                             |

| 11  | P3.6  | Digital I/O                                               | General I/O, ADC input ,OTP download                             |

| 12  | P3.5  | Digital I/O                                               | General I/O, ADC input ,OTP download                             |

| 13  | VPP   | Power supply                                              | Mode select and 6.5V power supply for OTP burning, or P12 output |

| 14  | P3.4  | Digital I/O                                               | General I/O, ADC input ,OTP download                             |

| 15 | P2.0 | Digital I/O | General I/O, or input for UART  |

|----|------|-------------|---------------------------------|

| 16 | P2.1 | Digital I/O | General I/O, or output for UART |

**Table 2 PIN definition**

## **FLIP51 Micro-Controller**

## 5.1 Instruction Set

The FLIP8051 is an improved option of the 80c51 microcontroller. It is 100% binary code upward compatible with the legacy 80c51.

Its pipeline architecture provides an increase of processing speed an average nine times, when running at the same clock frequency as a standard 80c51 real component.

## 5.2 MCU diagram

Figure 4 FIIP51 architecture

## 6 Development and download

The BK2461 have some different development and download methods. The working mode is decided by the VPP voltage when power up. The next table describes the different working mode.

| VPP<br>voltage | mode                       | description                                                                                                                    | Note                                                          |

|----------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|

| 6.5+-0.5       | OTP burning mode           | GPIO mapping to OTP download mode.                                                                                             | P3.4=spi_mosi<br>P3.5=spi_miso<br>P3.6=spi_clk<br>P3.7=spi_cs |

| 3+-0.5         | DEBUG mode                 | GPIO mapping to BIRD interface used to debug on chip. At this mode, the program can be loaded to the chip from JTAG interface. | P2.4=TDO<br>P2.5=TDI<br>P2.6=TMS<br>P2.7=TCK                  |

| 1.2+-0.5       | FLASH<br>download mode     | At this mode, BK2461 load program from the outside FLASH firstly, then run the loaded program                                  | P3.4=boot_si P3.5= boot_s0 P3.6= boot_sck P3.7= boot_csn      |

| 0+-0.5         | Normal mode (product mode) | At this mode, BK2461 run the program from the OTP directly.                                                                    |                                                               |

Table 3 work mode selection

## 7 FLIP8051 address space

#### 7.1 Overview

The memory organization of the Flip8051 is similar to that of standard 80C51. There are three separate memory spaces: CODE space (program memory), the XDATA space (external data memory) and the IDATA space (internal data memory).

These memory spaces shared the same address space but are accessed with different instruction types.

There are organized as follow for BK2461:

- ☐ CODE space: up to 8K Bytes of addressing range

- □ XDATA space: up to 512 Bytes of addressing range

- ☐ IDATA space: up to 256 Bytes.

Figure 5 FLIP51 SPACE

## 7.2 Program Memory (CODE space)

The Flip8051 has a 64K Bytes **CODE** space (8K for BK2461). Program memory is normally assumed to be read only and can be accessed only by MOVC instruction (or of course by the instruction fetch)

Two addressing modes are available for MOVC instructions:

☐ 16-bit data pointer (@A+DPTR).

The MOVC instructions use these indirect modes to access the current 64 K page of the code memory.

☐ 16-bit program counter (@A+PC).

The MOVC instruction uses this indirect mode to access the 64 K page of the code memory.

## 7.3 External Data Memory (XDATA space)

The **External Data memory** shares address bus with program memory. This data space can be up to 64K Bytes (512 for BK2461).

The external data memory can be accessed only by the standard MOVX instructions (plus some new instructions of the WHIRL instruction set)

Two addressing modes are available for MOVX instructions:

$\square$  Byte register (@Ri, i = 0,1).

Registers R0 and R1 indirectly address external data memory locations 00h-FFh. When MOVX instructions use this indirect mode, the MSB of the 16-bit address is filled with the content of MPAGE SFR (0A1h). Then, it allows MOVX @Ri instruction to access to 64K Bytes of external data memory. Usually, in 80C51 application, the Port 2 is used to this address extension. In order to keep software compatibility with existing 80C51 program, the register MPAGE is also updated by any value written at P2 register.

□ 16-bit data pointer (@DPTR).

The MOVX instructions use these indirect modes to access the page of the external data RAM pointed by the extended data pointer (DPX).

## 7.4 Internal Data Memory (IDATA space)

The **Internal data memory** is composed by 256 bytes of internal RAM and by a number of SFRs.

The main difference between these IDATA and XDATA spaces is the kind of instructions that enable to access to these memories. Most of the "data transfer" instructions are dedicated to access internal data memory (IDATA) since there are only four instructions (MOVX) dedicated to access external data memory. Moreover, only indirect addressing mode is available for XDATA whilst IDATA can be addressed by register, direct, register-indirect or immediate addressing mode. This provides a higher flexibility to access data. In addition, the Flip8051 memory interface with IDATA space is optimized and then access time to this space is faster than the access time of XDATA for both read/write operations.

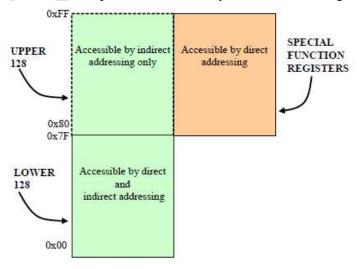

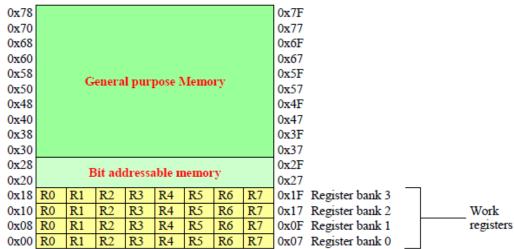

### 7.4.1 Internal Data memory organization

The internal data memory is divided into 3 spaces, which are referred to as the **Lower 128**, **Upper 128** and **SFR space**. Either direct or indirect addressing may be used to access the **lower 128** bytes of internal data memory. The **upper 128** bytes of internal data memory are accessible by indirect addressing only while direct addressing to region above 0x7F will access **SFR space**.

In the Flip8051, the SFRs are implemented internally to the model using Flip-Flops.

#### Figure 6 Internal Data memory

### 7.4.2 Internal ram: lower 128 byes

Figure 7 Internal Ram lower 128 bytes

The lower 128 bytes of Internal Data Memory is organized in three distinct areas: **0x00-0x1F**: The Register Banks are at the lowest 32 bytes of the internal data memory. Only one Register Bank is used at a time when an instruction uses R0 to R7. 2 bits in Processor Status Word (PSW), called RS1 and RS0, control the selection of the Register Bank. Bank 0 is selected upon reset. Indirect addressing mode used R0 and R1 as index registers **0x20-0x2F**: This memory space contains a general-purpose memory, which is bit addressable as well as byte addressable. The bit address ranged from 0 to 0x7F. When bit addressing is used in an instruction, the bit access in this region will occur. In this memory range, when bit addressing is used, bit address 0x00 is the bit 0 of address 0x20 while bit 7 of of the byte 0x20 has bit address 0x07. Bit address 0x7F is the bit 7 of address 0x2F. A bit access is different than a byte access by the type of instruction used.

**0x30-0x7F**: A general-purpose byte-addressable memory is located above address 0x30. It can be accessed both by direct or indirect addressing mode.

#### 7.4.3 Internal Ram: Upper 128 Bytes

The usage of the addresses between 0x80 and 0xFF is up to the user. This memory can be used for any purpose providing that indirect addressing mode is used when accessing this memory space, otherwise the Special Function Register memory will be accessed.

#### 7.4.4 The Stack and the stack pointer

The stack refers to an area of internal RAM that is used in conjunction with certain instructions (PUSH, POP) to store and retrieve data quickly. The Stack pointer register (SP, 0x81) is used to hold an internal RAM address that is called the "top of the stack". The data held in the SP register is the address in internal RAM where the last byte of data was stored by a stack operation. The reset value of Stack pointer register is 0x07 and can be changed to any internal RAM address by the programmer. Usually, the stack is located high in the RAM to avoid conflict with the work register, bit and byte area in internal RAM.

### 7.4.5 Special Function Registers

The direct-access data memory locations from 0x80 to 0xFF constitute the special function registers (SFRs). All the special function registers of the original 80C51 are present in the Flip8051. SFRs with addresses ending in 0x0 or 0x8 (e.g. P0, TCON, P1, SCON, IE, etc.) are bit-addressable as well as byte-addressable. All other SFRs are byte-addressable only.

The special function registers (SFRs) reside in their associated peripherals or in the core. The following tables shows the SFR address space with the SFR mnemonics and reset values. Unoccupied locations in the SFR space are unimplemented, i.e. no register exists. If an instruction attempts to write to an unimplemented SFR location, the instruction executes, but nothing is actually written. If an unimplemented SFR location is read, it returns an unspecified value

| A 11- 11- 11- 11- 11- 11- 11- 11- 11-                                                                         | unspecified value. |        |      |  |  |  |

|---------------------------------------------------------------------------------------------------------------|--------------------|--------|------|--|--|--|

| SFR bit7 bit6 bit5 bit4 bit3 bit2 Name                                                                        | bit1               | bit0   | addr |  |  |  |

|                                                                                                               |                    |        | 0x80 |  |  |  |

| SP                                                                                                            | -                  | -      | 0x81 |  |  |  |

| DPL                                                                                                           | -                  | -      | 0x82 |  |  |  |

| DPH                                                                                                           | -                  | -      | 0x83 |  |  |  |

| CKCON CKDIV1 CKDIV0 smod0 x x x                                                                               | x                  | х      | 0x84 |  |  |  |

| CLK_EN   adc_en   timer_en   uart_en   pwm_en   spi_en   i2c_en     CFG                                       | aes_mud_<br>en     | wdt_en | 0x85 |  |  |  |

| PCON2         SMOD         EUSB         CMD_RS         Latch_en         deep_sleep         OSC32k           T | RC32k              | IDLE   | 0x86 |  |  |  |

|                                                                                                               |                    |        | 0x87 |  |  |  |

| TCON TF1 TR1 TF0 TR0 IE1 IT1                                                                                  | IE0                | IT0    | 0x88 |  |  |  |

| TMOD GATE C/T M1 M0 GATE C/T                                                                                  | M1                 | MO     | 0x89 |  |  |  |

| TL0                                                                                                           | -                  | -      | 0x8A |  |  |  |

| TL1                                                                                                           | -                  | -      | 0x8B |  |  |  |

| THO                                                                                                           | -                  | -      | 0x8C |  |  |  |

| TH1                                                                                                           | -                  | -      | 0x8D |  |  |  |

| CCMCON                                                                                                        | -                  | -      | 0x8E |  |  |  |

| CCMVAL                                                                                                        | -                  | -      | 0x8F |  |  |  |

| P1                                                                                                            | -                  | -      | 0x90 |  |  |  |

|                                                                                                               |                    |        | 0x91 |  |  |  |

| DPSEL x x x x x x                                                                                             | х                  | DPSEL0 | 0x92 |  |  |  |

| P1IN_EN                                                                                                       | -                  | -      | 0x93 |  |  |  |

| P2IN_EN                                                                                                       | -                  | -      | 0x94 |  |  |  |

| P3IN_EN                                                                                                       | -                  | -      | 0x95 |  |  |  |

|                                                                                                               |                    |        | 0x96 |  |  |  |

BEKEN

|                            |     |     |     |                  |     |     |     | <u> </u> |                                                                            |

|----------------------------|-----|-----|-----|------------------|-----|-----|-----|----------|----------------------------------------------------------------------------|

| MMS                        | -   | -   | -   | -                | -   | -   | -   | -        | 0x97                                                                       |

| SCON0                      | SM0 | SM1 | SM2 | REN              | TB8 | RB8 | TI  | RI       | 0x98                                                                       |

| SBUF0                      | -   | -   | -   | -                | -   | -   | -   | -        | 0x99                                                                       |

|                            |     |     |     |                  |     |     |     |          | 0x9A                                                                       |

| PAGE_A<br>(NA)             | x   | X   | X   | х                | х   | х   | x   | X        | 0x9B                                                                       |

|                            | X   | Х   | Х   | X                | X   | Х   | X   | х        | 0x9C                                                                       |

|                            | X   | Х   | X   | X                | X   | Х   | X   | X        | 0x9D                                                                       |

| P1OUT_N                    | -   | -   | -   | -                | -   | -   | -   | -        | 0x9E                                                                       |

| P2OUT_N                    | -   | -   | -   | -                | -   | -   | -   | -        | 0x9F                                                                       |

| P2                         | -   | -   | -   | -                | -   | -   | -   | -        | 0xA0                                                                       |

| MPAGE                      | -   | -   | -   | -                | -   | -   | -   | -        | 0xA1                                                                       |

|                            |     |     |     |                  |     |     |     |          | 0xA2                                                                       |

|                            |     |     |     |                  |     |     |     |          | 0xA3                                                                       |

|                            |     |     |     |                  |     |     |     |          | 0xA4                                                                       |

| P3OUT_N                    | -   | -   | -   | -                | -   | -   | -   | -        | 0xA5                                                                       |

| WDT                        | x   | X   | X   | state            | Х   | ps2 | ps1 | ps0      | 0xA6                                                                       |

|                            |     |     |     |                  |     |     |     |          | 0xA7                                                                       |

|                            | EA  | X   | ET2 | ES               | ET1 | EX1 | ET0 | EX0      | 0xA8                                                                       |

| IE                         | LA  |     |     |                  |     |     |     |          |                                                                            |

| IE                         | LA  |     |     |                  |     |     |     |          | 0xA9                                                                       |

| P1_PU                      | -   | -   | -   | -                | -   | -   | -   | -        | 0xA9<br>0xAA                                                               |

| P1_PU<br>P2_PU             | -   | -   | -   | -                | -   | -   | -   | -        | 0xA9<br>0xAA<br>0xAB                                                       |

| P1_PU                      | -   | -   | -   | -                | -   | -   | -   | -        | 0xA9<br>0xAA<br>0xAB<br>0xAC                                               |

| P1_PU<br>P2_PU             | -   | -   | -   | -                | -   | -   | -   | -        | 0xA9<br>0xAA<br>0xAB<br>0xAC<br>0xAD                                       |

| P1_PU<br>P2_PU<br>P3_PU    | -   | -   | -   | -                | -   | -   | -   | -        | 0xA9<br>0xAA<br>0xAB<br>0xAC<br>0xAD                                       |

| P1_PU<br>P2_PU<br>P3_PU    | -   | -   | -   | -                | -   | -   | -   | -        | 0xA9 0xAA 0xAB 0xAC 0xAD 0xAE                                              |

| P1_PU<br>P2_PU<br>P3_PU    | -   | -   | -   | -                | -   | -   | -   | -        | 0xA9 0xAA 0xAB 0xAC 0xAD 0xAE 0xAF                                         |

| P1_PU<br>P2_PU<br>P3_PU    | -   | -   | -   | -                | -   | -   | -   | -        | 0xA9 0xAA 0xAB 0xAC 0xAD 0xAE 0xAF 0xB0 0xB1                               |

| P1_PU<br>P2_PU<br>P3_PU    | -   | -   | -   | -                | -   | -   | -   | -        | 0xA9 0xAA 0xAB 0xAC 0xAD 0xAE 0xAF 0xB0 0xB1 0xB2                          |

| P1_PU P2_PU P3_PU P1_PD P3 | -   | -   | -   | -                | -   | -   | -   | -        | 0xA9 0xAA 0xAB 0xAC 0xAD 0xAE 0xAF 0xB0 0xB1 0xB2 0xB3                     |

| P1_PU P2_PU P3_PU P1_PD P3 |     |     | -   |                  | -   | -   |     | -        | 0xA9 0xAA 0xAB 0xAC 0xAD 0xAE 0xAF 0xB0 0xB1 0xB2 0xB3                     |

| P1_PU P2_PU P3_PU P1_PD P3 | -   | -   | -   | -                | -   | -   | -   | -        | 0xA9 0xAA 0xAB 0xAC 0xAD 0xAE 0xAF 0xB0 0xB1 0xB2 0xB3 0xB4 0xB5           |

| P1_PU P2_PU P3_PU P1_PD P3 |     |     | -   |                  | -   | -   |     | -        | 0xA9 0xAA 0xAB 0xAC 0xAD 0xAE 0xAF 0xB0 0xB1 0xB2 0xB3 0xB4 0xB5           |

| P1_PU P2_PU P3_PU P1_PD P3 |     |     | -   |                  | -   | -   |     | -        | 0xA9 0xAA 0xAB 0xAC 0xAD 0xAE 0xAF 0xB0 0xB1 0xB2 0xB3 0xB4 0xB5 0xB6 0xB7 |

| P1_PU P2_PU P3_PU P1_PD P3 |     |     | -   |                  | -   | -   |     | -        | 0xA9 0xAA 0xAB 0xAC 0xAD 0xAE 0xAF 0xB0 0xB1 0xB2 0xB3 0xB4 0xB5 0xB6 0xB7 |

| P1_PU P2_PU P3_PU P1_PD P3 |     |     |     | -<br>-<br>-<br>- |     | -   |     |          | 0xA9 0xAA 0xAB 0xAC 0xAD 0xAE 0xAF 0xB0 0xB1 0xB2 0xB3 0xB4 0xB5 0xB6 0xB7 |

| BEK | ΕN |

|-----|----|

|     |    |

|     |    |

|                       |     |                        |              |             |          |              |          |              | <u> </u> |

|-----------------------|-----|------------------------|--------------|-------------|----------|--------------|----------|--------------|----------|

|                       |     |                        |              |             |          |              |          |              | 0xBB     |

|                       |     |                        |              |             |          |              |          |              | 0xBC     |

|                       |     |                        |              |             |          |              |          |              | 0xBD     |

|                       |     |                        |              |             |          |              |          |              | 0xBE     |

|                       |     |                        |              |             |          |              |          |              | 0xBF     |

| AIF                   | -   | -                      | -            | -           | -        | -            | -        | -            | 0xC0     |

|                       |     |                        |              |             |          |              |          |              | 0xC1     |

|                       |     |                        |              |             |          |              |          |              | 0xC2     |

|                       |     |                        |              |             |          |              |          |              | 0xC3     |

|                       |     |                        |              |             |          |              |          |              | 0xC4     |

|                       |     |                        |              |             |          |              |          |              | 0xC5     |

|                       |     |                        |              |             |          |              |          |              | 0xC6     |

|                       |     | <b>5</b> \/ <b>5</b> 0 | 5011         | <b>TOLI</b> |          | <b>TD</b> •  | 070      | 00010        | 0xC7     |

| T2CON                 | TF2 | EXF2                   | RCLK         | TCLK        | EXEN2    | TR2          | CT2      | CPRL2        | 0xC8     |

|                       |     |                        |              |             |          |              |          |              | 0xC9     |

| RCAP2L                | -   | -                      | -            | -           | -        | -            | -        | -            | 0xCA     |

| RCAP2H                | -   | -                      | -            | -           | -        | -            | -        | -            | 0xCB     |

| TL2                   | -   | -                      | -            | -           | -        | -            | -        | -            | 0xCC     |

| TH2                   | -   | -                      | -            | -           | -        | -            | -        | -            | 0xCD     |

|                       |     |                        |              |             |          |              |          |              | 0xCE     |

|                       |     |                        |              |             |          |              |          |              | 0xCF     |

| PSW                   | -   | -                      | -            | -           | -        | -            | -        | -            | 0xD0     |

|                       |     |                        |              |             |          |              |          |              | 0xD1     |

| I2CM<br>Data_ie       | X   | X                      | ETBE         | X           | ETBF     | ERBE         | X        | ERBF         | 0xD2     |

|                       |     |                        |              |             |          |              |          |              | 0xD3     |

| I2CM<br>CALLADD<br>R0 | RWN | CADDR[6]               | CADDR[<br>5] | CADDR[4]    | CADDR[3] | CADDR[<br>2] | CADDR[1] | CADDR[<br>0] | 0xD4     |

|                       |     |                        |              |             |          |              |          |              | 0xD5     |

|                       |     |                        |              |             |          |              |          |              | 0xD6     |

|                       |     |                        |              |             |          |              |          |              | 0xD7     |

|                       |     |                        |              |             |          |              |          |              | 0xD8     |

| P1_OPDR               | -   | -                      | -            | -           | -        | -            | -        | -            | 0xD9     |

| P2_OPDR               |     | -                      | -            | -           | -        | -            | -        | -            | 0xDa     |

| P3_OPDR               | -   | -                      | -            | -           | -        | -            | -        | -            | 0xDb     |

|                       |     |                        |              |             |          |              |          |              | 0xDc     |

|                       |     |                        |              |             |          |              |          |              | 0xDd     |

|                       |     |                        |              |             |          |              |          |              | 0xDe     |

BEKEN

| ACC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                 |   |   |      |          |       |      |          |        | <u>/                                    </u> |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|---|---|------|----------|-------|------|----------|--------|----------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                 |   |   |      |          |       |      |          |        | 0xDf                                         |

| CTRL   12CM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ACC             | - | - | -    | -        | -     | -    | -        | -      | 0xE0                                         |

| IZCM   RXDATA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                 | х | х | WAIT | х        | STOP  | SRST | STA      | BUSY   | 0xE1                                         |

| TXDATA   12CM   PRESC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | I2CM            | - | - | -    | -        | -     | -    | -        | -      | 0xE2                                         |

| IZCM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | I2CM            | - | - | -    | -        | -     | -    | -        | -      | 0xE3                                         |

| IZCM   TXRX_ST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | I2CM            | - | - | -    | -        | -     | -    | -        | -      | 0xE4                                         |

| IZCM   X                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | I2CM<br>TXRX_ST |   | x | X    | DNA      | SANA  | UNF  | OVF      | NEND   | 0XE5                                         |

| TXXX_IE     Ale     Al | I2CM<br>DATA_ST | х | х | TBE  | х        | TBF   | RBE  | х        | RBF    | 0XE6                                         |

| PALTO                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                 | X | X | X    | EDNA     | ESANA | EUNF | EOVF     | ENEND  | 0xE7                                         |

| EXSLEEP X X X X X X X X X X Exsleep2 0xE  P1_WUEN 0xE  P2_WUEN 0xE  P3_WUEN 0xE  B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | AIE             | - | - | -    | -        | -     | -    | -        | -      | 0xE8                                         |

| P1_WUEN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | PALT0           | х | x |      | T2_IN_EN |       |      | N        | EN     | 0xE9                                         |

| P1_WUEN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | EXSLEEP         | X | X | Х    | X        | X     | Х    | exsleep2 |        | 0xEA                                         |

| P2_WUEN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                 |   |   |      |          |       |      |          |        | 0xEB                                         |